ASML拟于2030年推出Hyper-NA EUV光刻机

近年来,随着半导体尖端制程工艺越来越逼近物理极限,荷兰光刻机大厂ASML生产的EUV光刻机已经成为了继续推动晶体管微缩的关键设备,而当制程工艺进入2nm以下的埃米时代,可能就需要用到售价高达3.5亿欧元的High NA EUV(0.55NA)光刻机。

在2023年底,ASML已经开始向英特尔交付了首套High NA EUV光刻机,英特尔也于近期完成了组装。虽然,High NA EUV光刻机刚开始出货,但是ASML已经在加紧研发新一代的Hyper-NA EUV光刻机,为其寻找合适的解决方案。根据EETimes报导,ASML近期公布了还处于开发早期阶段的Hyper NA EUV光刻机的技术蓝图,预计最快将会在2030年推出。

Hyper NA EUV光刻机2030年推出

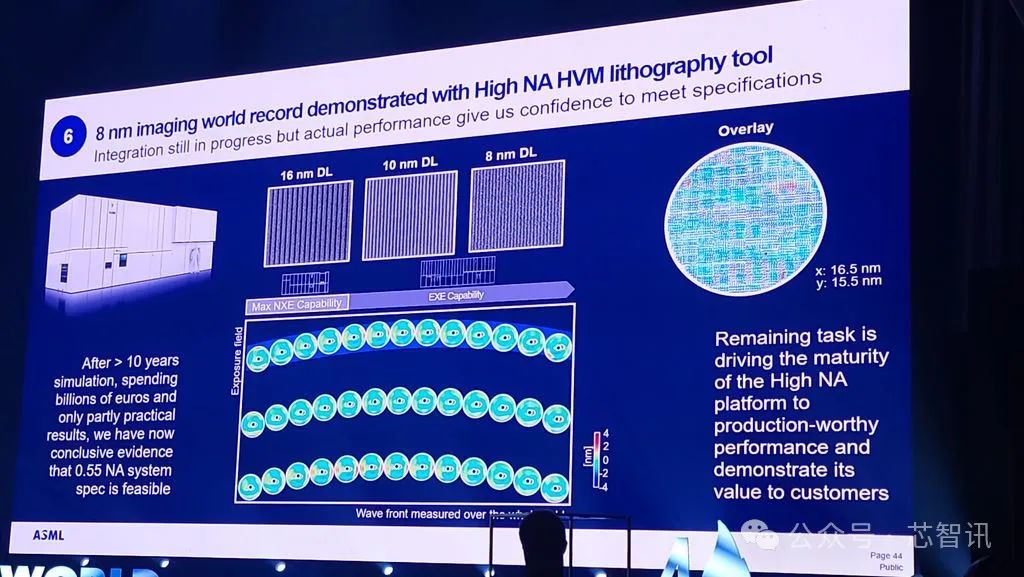

ASML前总裁兼首席技术官、现任公司顾问Martin van den Brink在2024年5月举行的imec ITF World的演讲中宣布,ASML已经可用其试验性质的High NA EUV(EXE:5200)光刻机打印生产8nm线宽,这是的新纪录,这打破了该公司在4月初当时创下的记录(10nm线宽),而且还具有一定程度的重叠覆盖。Martin van den Brink强调,ASML当前已经取得了出色的进展,因此,对High NA EUV光刻机的发展充满信心,预计未来将能够继续突破其极限。

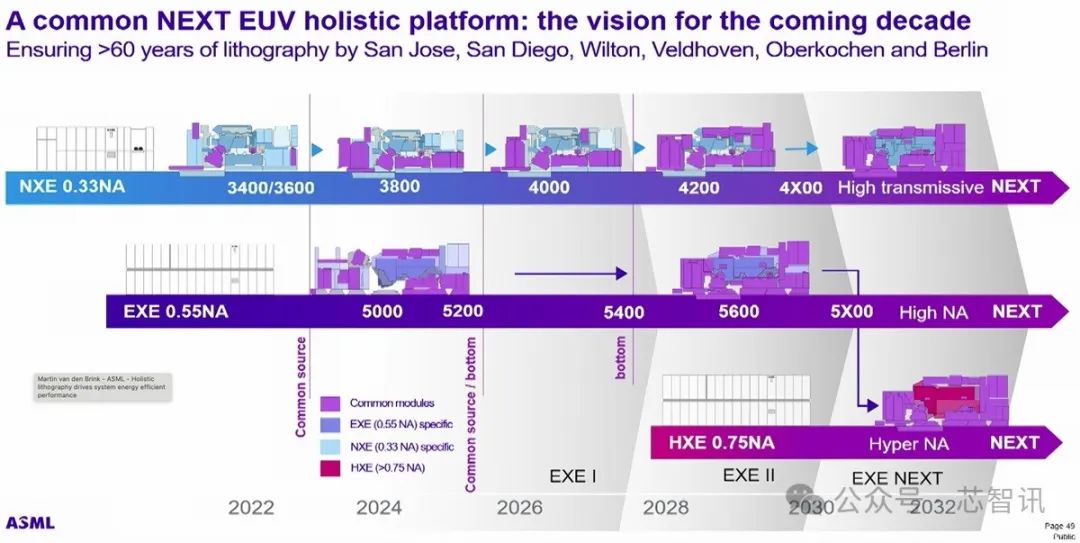

同时,Martin van den Brink还透露,ASML计划在2030年左右正式推出Hyper NA EUV光刻机,其数值孔径(NA)将达到0.75,以便实现更高分辨率的图案化及更小的晶体管特征。相较之下,High NA EUV光刻机的数值孔径为0.55,标准EUV光刻机则是0.33。对于ASML而言,“十年后,我们将拥有一个Low NA、High NA 和 Hyper NA 的共用的单一EUV平台”,借此可以进一步改善成本和交货时间。

从最新曝光的ASML光刻机路线图来看,0.75NA的Hyper NA EUV光刻机的型号的前缀为“HXE”,预计首款产品将会在2030年前后推出。

imec图案化项目总监Kurt Ronse也感叹道,这是 ASML 首次将 Hyper NA EUV光刻机添加到其产品路线图当中。

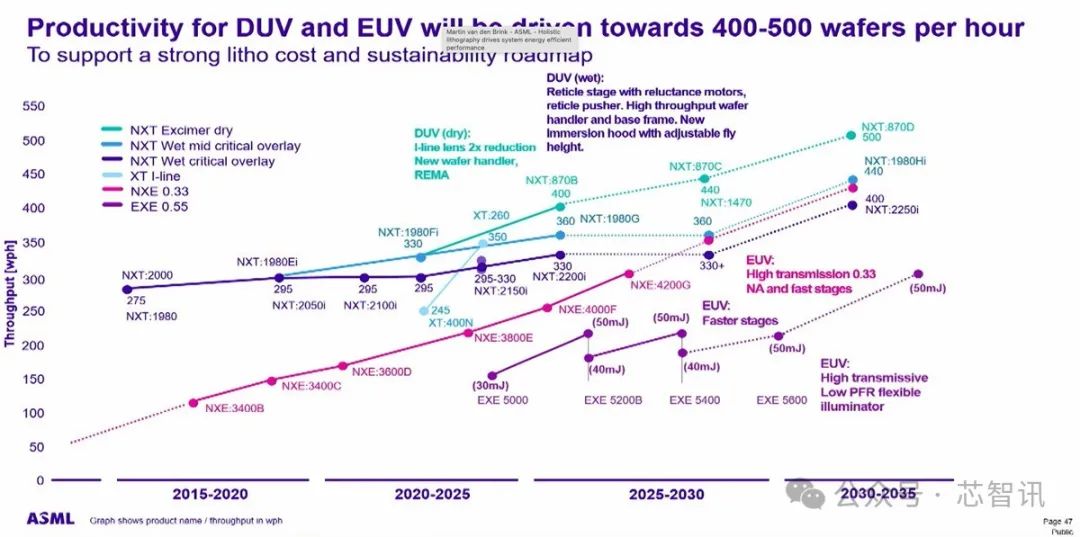

从设备生产效率的路线图来看,ASML刚刚出货的High NA EUV光刻机(EXE:5000),目前的生产速度仅每小时150片晶圆,预计到2026年左右,将会提升到每小时约200片晶圆,届时也会推出第二代的High NA EUV光刻机(EXE:5200B),2028年前后会推出第三代的High NA EUV光刻机(EXE:5400),2030年前后将会推出更高速的第四代High NA EUV光刻机(EXE:5600),将采用高透射率、低PFR的柔性发光器。后续到2035年前后,新的High NA EUV光刻机产能将会提高到每小时300片晶圆,达到目前出货的High NA EUV光刻机(EXE:5000)产能的2倍。但是该路线图并未透露Hyper NA EUV光刻机的生产效率数据,不过考虑到Hyper NA EUV光刻的机的复杂度及面临的更多的挑战,预计初期的产能将会低于每小时200片晶圆。

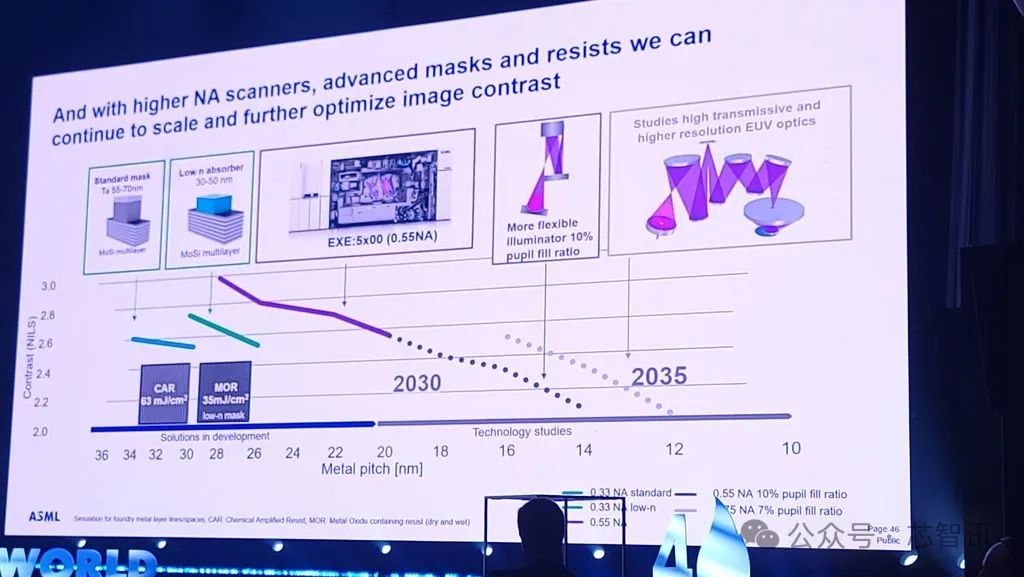

从支持的工艺节点来看,根据Martin van den Brink 此前披露的未来15年的逻辑器件的工艺路线图来看,利用目前的0.3NA的标准型EUV光刻机支持到2025年2nm的量产,再往下就需要通过多重曝光技术来实现,但支持到2027年量产的1.4nm将会是极限。而0.55NA的High NA EUV光刻机则可以支持到2029年1nm制程的量产,如果采用多重曝光,则可以支持到2033年量产的5埃米(0.5nm)制程节点,再往下就可能必须要采用0.75NA的Hyper NA EUV光刻机,或许可以支持到2埃米(0.2nm)以下的制程节点,这里路线图上打了一个问号,所以不确定Hyper NA EUV光刻机能否支持下去。

这里需要强调的是,虽然一个硅原子的直径大概就在1埃米左右,但是这里的所有的制程节点命名都只是等效指标,并不是真实的物理指标。2埃米制程节点的对应的晶体管的金属间距为大约在16-12nm,进入到2埃米以下制程以下,金属间距才会进一步缩小到14-10nm。

当然,这里光有先进的先进的光刻机是不够的,还需要先进的掩模和光刻胶,以及更复杂的晶体管架构来进行支持,这需要大量的研发资金投入。

目前,其他使用 EUV 光刻机的领先芯片制造商,如三星、美光和 SK 海力士,也在考虑High NA EUV光刻机。台积电可能也会提前使用这项技术。ASML上周暗示,可能将在2024年底前向台积电出货High NA EUV光刻机。

Ronse 表示:“High NA 应该会持续贯穿从 2nm 到 1.4nm、10埃米甚至7埃米的工艺节点。”他补充说,此后,Hyper NA 将开始占据主导地位。

Hyper NA EUV面临的挑战

“imec 在两年前就已经开始利用计算机模拟研究 Hyper NA。目前有很多研究正在进行,我们能把NA提高到 0.55 以上,未来能达到 0.75、0.85 吗?Hyper NA肯定会带来一些新挑战。”作为与 ASML 合作开发光刻技术已有 30 多年的老将,Kurt Ronse分析道:“其中一个挑战是,光的偏振从 0.55 NA 左右开始。如果高于 0.55 NA,你很快就会发现偏振正在破坏对比度,因为偏振方向之一基本上抵消了光线,你需要偏振器来避免这种情况。”但是,偏振器的缺点是阻挡光线、降低能效并增加生产成本。

“Hyper NA 的另一个挑战是光刻胶。在 0.55 NA 时,我们就已经将光刻胶变薄了。而Hyper NA 的情况则更糟。这将给蚀刻选择性带来更多挑战。”Kurt Ronse说道。

虽然ASML已经向英特尔交付了首台High NA EUV光刻机,但英特尔目前只是将High NA EUV光刻机用于其Intel 18A工艺的测试,以积累相关经验,后续要等到2026年才会被用于Intel 14A的量产。另外台积电高管此前也曾公开表示,High NA EUV光刻机太过昂贵,台积电依靠现有的常规EUV光刻机能力可支持到2026年的A16制程量产。

Ronse 表示:“台积电目前还不需要High NA EUV光刻机,它可以将其在双重图案化方面的专业知识与现有的 EUV 工具结合起来。双重曝光中真正关键的是边缘位置误差,两个掩模必须完全对齐。而且双重图案化,意味着必须把所有事情都做两遍,这很容易导致成本增加。”Ronse 补充道:“英特尔希望避免这种情况,他们可能没有像台积电那样掌握EUV双重曝光。因此,他们更喜欢使用High NA EUV 来实现更高的分辨率。”

Martin van den Brink 在 Imec ITF World论坛上表示:“Hyper NA 这种分辨率更高的工具对于减少工艺步骤至关重要,从而降低处理晶圆所需的成本和能源。“Hyper NA 让我们远离双重图案化的危险复杂性,”Martin van den Brink 说道。

Hyper NA之后,未来在哪?

Martin van den Brink在2022年接受媒体采访时就曾表示,Hyper NA可能将是最后一个NA,而且不一定能真正投入生产,这意味经过数十年的光刻技术创新,我们可能会走到当前半导体光刻技术之路的尽头。即使Hyper NA能够实现,但是如果采用Hyper NA技术的制造成本增长速度和目前High NA EUV技术一样(单台设备价格高达3.5亿欧元),那么经济层面几乎是不可行的。

不过,Martin van den Brink于2023年再次谈到Hyper NA EUV技术之际,似乎增加了很多的信心,认为Hyper NA EUV将是一个机会,将成为2030年之后的新愿景。在最新的演讲当中,Martin van den Brink认为,未来Hyper NA EUV相比High NA EUV上采用双重曝光的成本将会更低。

从其他技术路线来看,虽然佳能推出了纳米压印技术,希望能够在某种程度上替代EUV光刻机,但是其生产率通常远低于High NA EUV光刻机。还有一种想法是,多束电子束光刻技术,它通过将图案直接写入硅晶圆来消除使用昂贵的光掩模。唯一一家开发电子束光刻工具的公司——总部位于荷兰的 Mapper 公司已经倒闭。

显然,一旦未来Hyper NA也无路可走,那么就几乎没有其他替代品了。

“你无法想象会存在只有2埃米的器件,”Ronse 说道。“它只有两个原子大小。在某个时候,现有的光刻技术路线必然会终结。”

“或许新材料可能会取代硅。有些新材料具有更高的电子迁移率,”Ronse 说道。“但这些材料很难放到硅晶圆上。研究小组正在研究这个问题。只有在电子必须通过的几个层面上,你才需要沉积一层非常薄的新材料层。我们需要的是能够在整个晶圆上均匀沉积该材料曾的专用设备。目前,它还在实验室里。我们只在小范围内进行研究。将会有新的沉积设备。此外,蚀刻这些材料可能更加困难,因此我们需要新的蚀刻技术。”

首 页

首 页 关于我们

关于我们 新闻资讯

新闻资讯 行业政策

行业政策 企业评估

企业评估 会员中心

会员中心 协会刊物

协会刊物 人力资源

人力资源 合作交流

合作交流