西班牙,首款RISC-V芯片

最近,巴塞罗那超级计算中心-国家超级计算中心 (BSC-CNS) 展示了新型 Sargantana 芯片,这是完全由 BSC 设计的第三代开源处理器。Sargantana的开发是巩固BSC在欧洲RISC-V开源计算技术研究领先地位的关键一步。

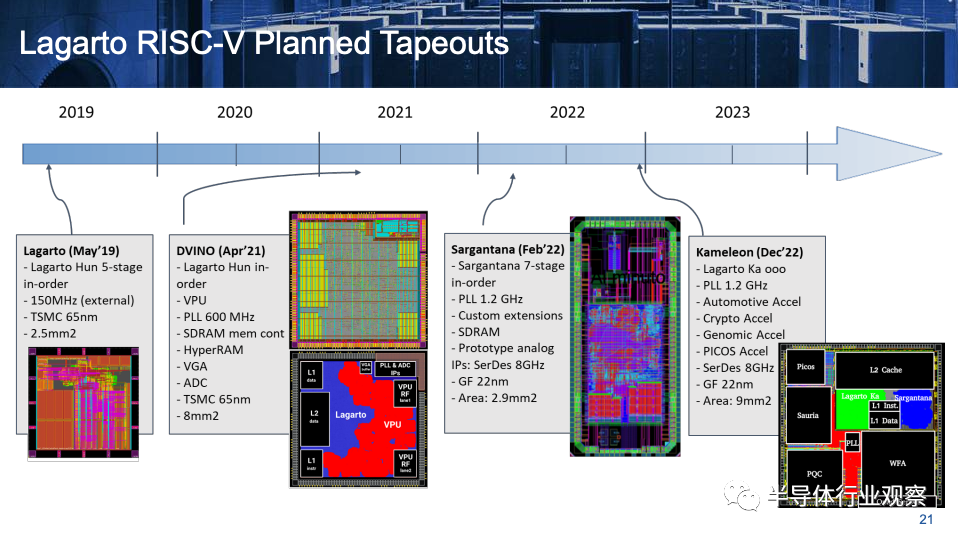

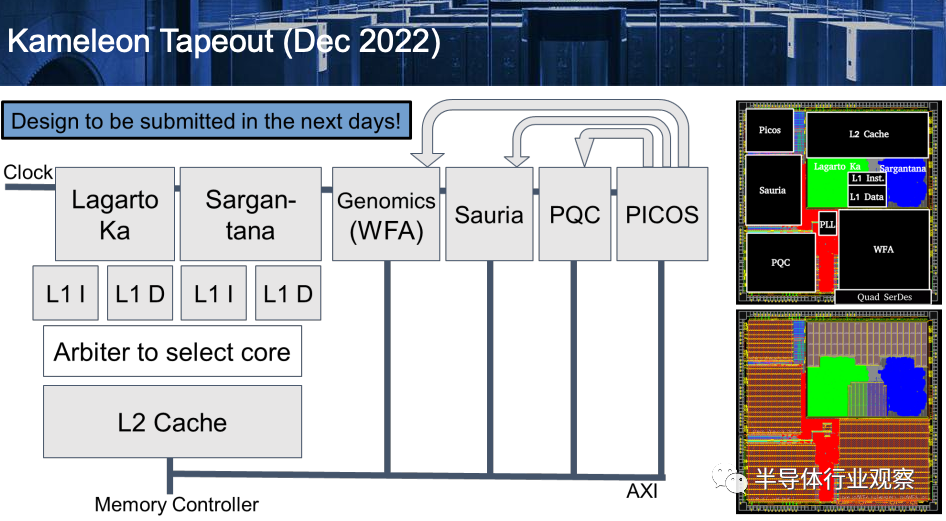

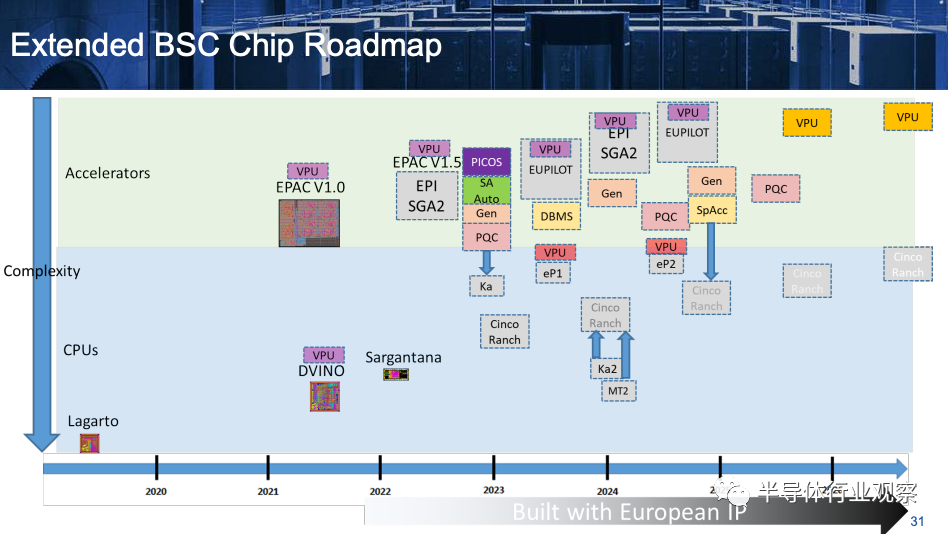

Sargantana(阿拉贡语和加泰罗尼亚语中蜥蜴的名字)是第三代 Lagarto 处理器,是西班牙在 DRAC 项目(为下一代计算机设计基于 RISC-V 的加速器)框架内开发的首款开源芯片,是欧洲学术层面最先进的开源芯片之一。新款 Sargantana 比其两款前辈 Lagarto Hun (2019) 和 DVINO (2021) 具有更好的性能,并且是 Lagarto 系列中首款突破千兆赫工作频率障碍的处理器。

事实上,这些新处理器的指令集架构 (ISA) 是开源的,因此非专有且可供所有人使用,通过公司和机构的协作实现创新,不受专有技术的限制,从而减少了对大型跨国公司的技术依赖。这些新芯片所基于的RISC-V自由硬件架构可能会像Linux在软件世界中带来的技术革命一样,在硬件世界中带来一场技术革命。

“Sargantana 的推出是欧洲基于 RISC-V 技术的开发又向前迈出了一步,该技术是未来欧洲高性能处理器的雏形。这种开放硬件对于确保技术主权和保持欧洲工业竞争力至关重要,并巩固 BSC 作为欧洲引入芯片设计开源先锋的角色。”BSC 主任 Mateo Valero 说道。

2017年,欧盟将缺乏自己的硬件确定为主要漏洞之一,因为过度依赖欧洲以外(尤其是美国、台湾、中国)设计和生产的芯片会带来工业间谍活动的风险。日本和韩国。随后,BSC 受欧盟委托,领导未来欧洲芯片的科学开发,为市场提供开放的本地替代方案,适用于高性能计算、人工智能、汽车行业和物联网。

报道指出,来自其他大学和研究中心的研究人员,例如墨西哥国立理工大学计算研究中心 (CIC-IPN)、国家微电子中心 (CNM-CSIC)、加泰罗尼亚理工大学 (UPC)、自治大学巴塞罗那大学 (UAB)、巴塞罗那大学 (UB) 和罗维拉伊维尔吉利大学 (URV) 参与了 Sargantana 的开发。

该项目由 BSC 研究员 Miquel Moretó 协调,他强调了开源半导体设计在促进世界各地公司和学术机构之间合作方面的优势。他说:“新的 Sargantana 芯片向所有人免费提供,通过开放协作开启处理器创新的新时代,任何人、任何地方都可以从 RISC-V 技术中受益。”

Moretó指出,Sargantana是一款实验芯片,一种研究原型,可以让我们测试RISC-V技术的应用并加深我们的知识,但它尚未设计用于计算机或其他设备。Moretó 补充道:“我们正在开发一项技术,该技术将使西班牙和欧洲能够在未来设计自己的竞争力日益增强的处理器,此外还可以培训该领域的未来专业人员,这无疑将为生产链增加巨大价值。”加泰罗尼亚、西班牙和欧洲共同努力,在巴塞罗那制造欧洲技术并培训该领域的工程师。

这一目标与Mateo Valero提出的让Barcelona成为处理器设计国际标杆的想法是一致的。瓦莱罗表示:“我们拥有巴塞罗那及其周边地区所需的人才、技术知识和科学环境,使其能够与世界上任何机构或地区竞争,成为推动公司创建和新就业机会的设计谷” 。

Sargantana项目获得了半导体行业战略转型项目(PERTE Chip)的资金,该项目是西班牙政府批准的所有工业转型项目中最大的投资,以及加泰罗尼亚ERDF运营计划2014-2020的欧洲资金,在加泰罗尼亚政府的支持下。

Sargantana 颁奖仪式在巴塞罗那的 BSC 设施举行,是西班牙开放硬件联盟 (SOHA) 第一天的一部分,该联盟汇集了西班牙大学和研究中心,旨在促进开放计算机领域的研究技术和建筑,从而有助于人才培训,创造高质量的就业机会。

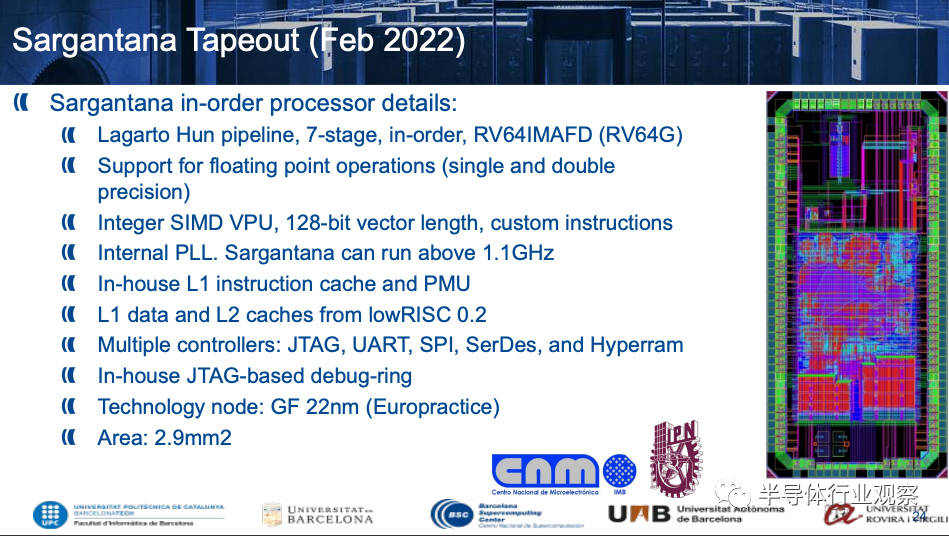

资料显示,第三代 Lagarto 处理器系列由 GlobalFoundries 22 纳米技术节点进行制造。该设计基于开源指令集架构(ISA)RISC-V,是来自BSC、CIC-IPN、CNM、UAB、UB、UPC和URV的研究人员联合开发的设计。

这种新设计称为 Sargantana,并将 Lagarto 标量核心与多个模拟 IP 集成在一起。Sargantana 是 Lagarto 系列中第一个打破千兆赫频率壁垒的装配式设计。

Sargantana 相对于 Lagarto 系列第二代 DVINO 的主要新颖之处:

-

新的有序核心设计在模拟基准测试中预计 IPC 提高 36%。

-

更深的管道设计,在典型拐角处达到 1.2GHz。

-

添加了对单浮点和双浮点的支持(F 和 D RISC-V 扩展)。

-

添加了新的 128 位 SIMD 矢量处理单元 (VPU),用于整数和自定义基因组矢量指令。

-

非阻塞内存访问,最多有 16 次misses(最多 2 次高速缓存块未命中)。

-

添加了新的高速 SerDes 内存控制器(2 至 8 Gbps)。

-

添加了自定义 bootROM 控制器。

-

添加了具有闪烁噪声消除功能和 AXI4-Lite 标准总线接口的定制 16 位高分辨率模数转换器 (ADC) IP。

-

添加了用于随机数生成的定制单光子雪崩二极管 (SPAD) IP。

Sargantana 处理器详细信息:

-

Lagarto Hun 标量管道,7 级,有序,RV64IMAFD ISA,特权 ISA 1.11。

-

用于基因组学的整数 VPU,128 位向量长度,向量 ISA 0.7.1。

-

集成片上整数锁相环 (PLL) 设计和仿真运行频率为 600MHz 至 2.2GHz。

-

内部L1指令缓存和PMU(性能监控单元)。

-

来自 Untethered lowRISC 版本 0.2 的 L1 数据和 L2 缓存。

-

多个重要的外设控制器:JTAG、UART、SPI、bootROM、SerDes 和 HyperRAM。

-

基于 JTAG 的内部调试环。

-

技术节点:GF 22nm。

-

面积:2.89mm²。

首 页

首 页 关于我们

关于我们 新闻资讯

新闻资讯 行业政策

行业政策 企业评估

企业评估 会员中心

会员中心 协会刊物

协会刊物 人力资源

人力资源 合作交流

合作交流